汕大计组复习提纲2017版

本文最后更新于:December 27, 2017 pm

汕大计算机系2017年的计组课最后期末的复习提纲,我个人整理各类资料和PPT总结,有部分可能会有错漏或不足,这里分享给有需要的同学。

01讲

词汇

ACM:Association for Computing Machinery,美国计算机协会

ENIAC:Electronic Numerical Integrator And Computer,电子数字积分计算机

ALU:算术逻辑部件,Arithmetic and Logical Unit

CP:时钟,Clock Pulse

ISA:Instruction Set Architecture,指令集体系结构(指令集架构)

LSIC:大规模集成电路(Large Scale Integrated circuits

MOOC:massive open online courses,大型开放式网络课程

两个PC:Person Computer, Program Counter

PLC:可编程逻辑控制器,Programmable Logic Controller

问题:

1.计算机系统是?

计算机系统=硬件/固件+软件

2.固件是什么?

① 固化的程序(firmware),例如计算机主板上的BIOS。

② 固件一般存储于设备中的电可擦除只读存储器EEPROM(Electrically Erasable Programmable ROM)或FLASH芯片中,一般可由用户通过特定的刷新程序进行升级的程序。

③ 固件常见于:手机、数码相机、mp3、mp4、路由器、交换机、U盘、主板的BIOS(BIOS就是一种固件)、显卡的BIOS。

3.什么是“软件摩尔定律”?

软件摩尔定律:每18个月,软件体积大一倍,效率差一半。

4.冯·诺依曼体系和哈佛总线体系的区别?

程序空间和数据空间是否是一体的。

冯·诺依曼结构数据空间和地址空间不分开,哈佛结构数据空间和地址空间是分开的。

5.冯.诺依曼计算机体系的主要特点 ?

① 计算机由运算器、控制器、存储器、输入设备和输出设备五部分组成;

② 采用存储程序的方式;

③ 数据以2进制表示。

6.计算机系统结构概念的实质?

确定计算机系统中软硬件的界面,界面之上是软件实现的功能,界面之下是硬件和固件实现的功能。

02讲(数制和编码、整数的表示)

问题:

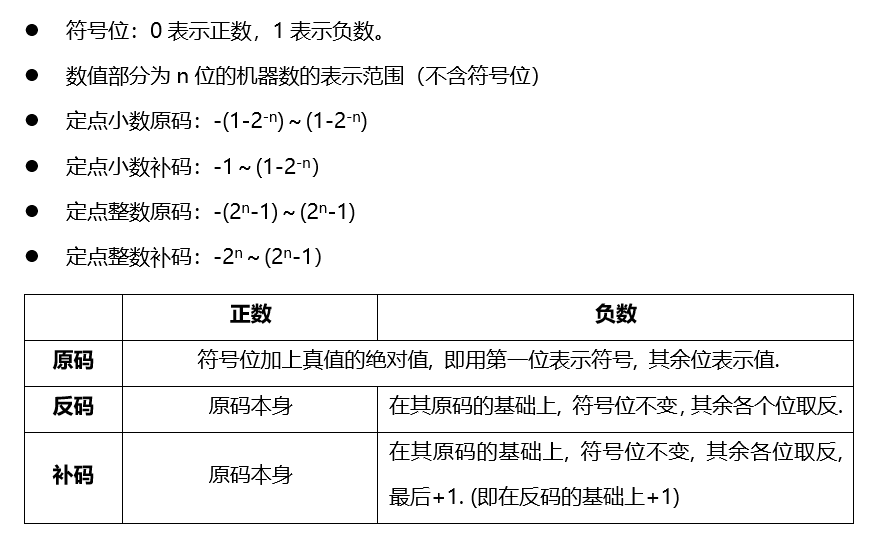

1.定点整数的原、反、补码表示?

小数点位置约定再固定位置的数称为定点数;小数点位置约定为可浮动的数称为浮点数。对于定点整数,其小数点总是固定在数的最右边,因此可用定点整数来表示整数。

03讲(浮点数-数据的宽度和存储)

词汇

IEEE:Institute of Electrical and Electronics Engineers,电气和电子工程师协会

MSB(msb),Most Significant Bit,最高有效位。或Most Significant Byte,最高有效字节。

LSB(msb),least significant bit,最低有效位。或least significant byte,最低有效字节。

问题:

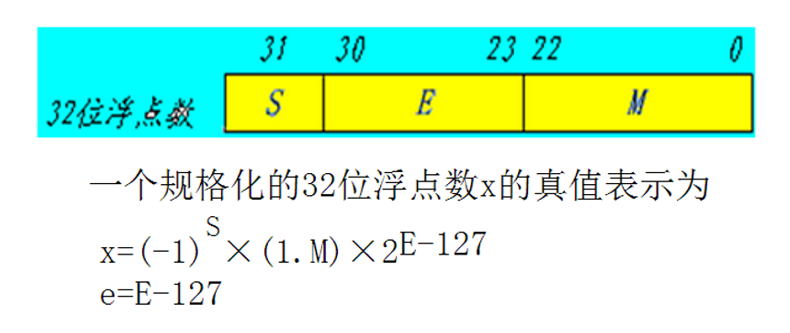

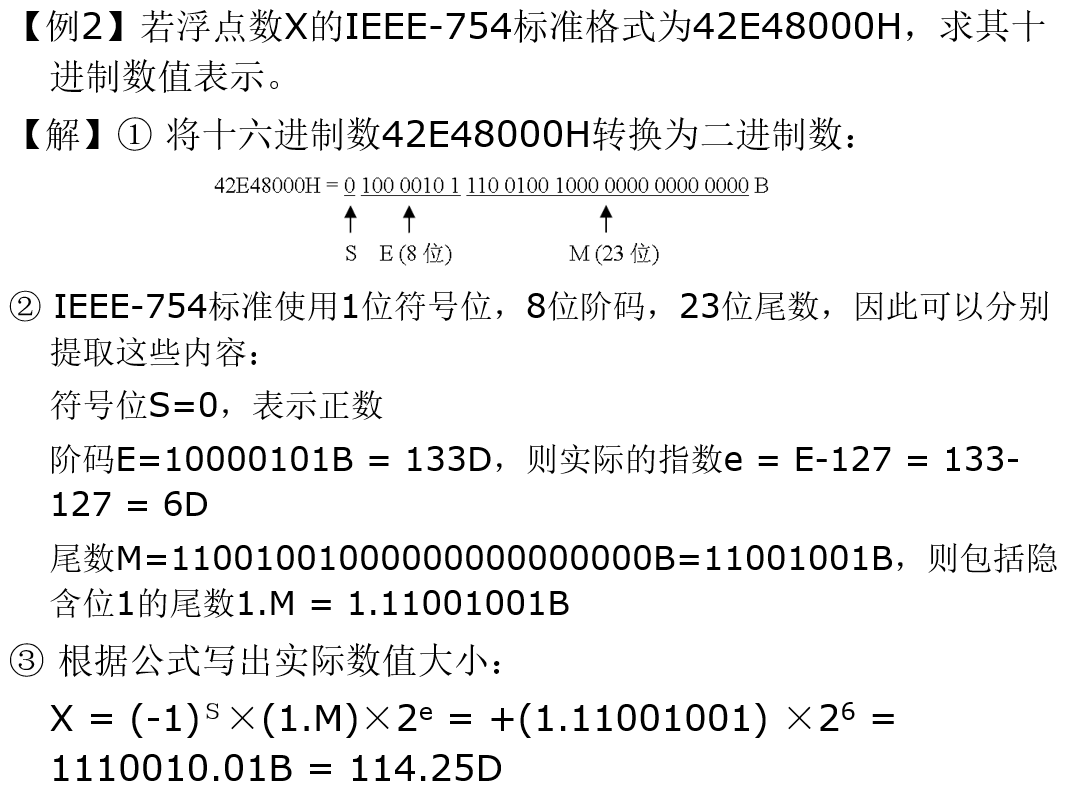

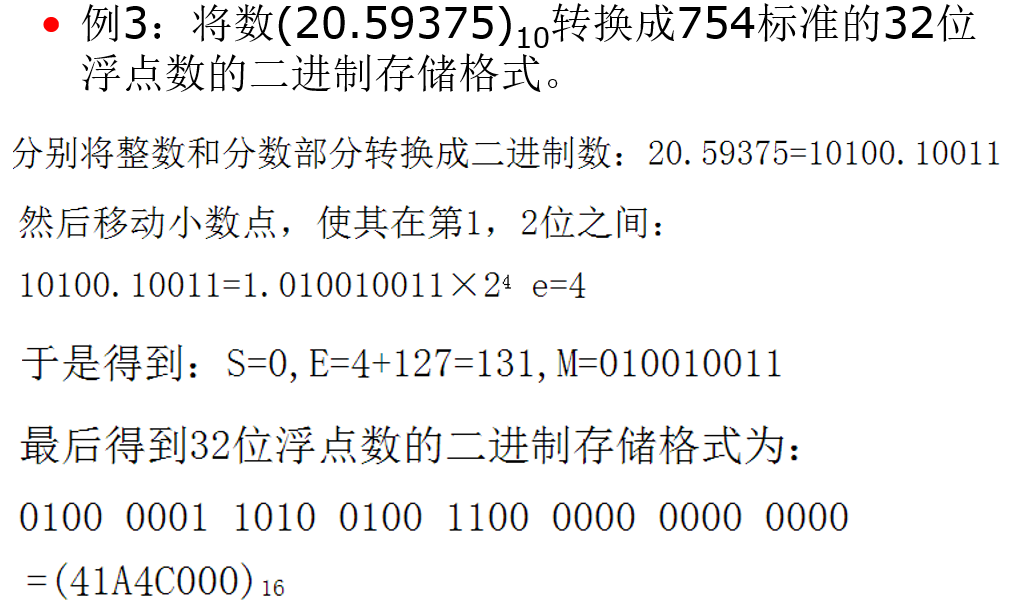

1.IEEE754标准32位浮点数的表示?

2.大端方式与小端方式?

- 大端是高低结合;大端方式将数据的最高有效字节存放在低地址单元中,将最低有效字节存放在高地址单元中,即数据的地址就是MSB所在的地址。

- 小端是高高结合;小端方式将数据的最高有效字节存放在高地址单元中,将最低有效字节存放在低地址单元中,即数据的地址就是LSB所在的地址。

- 最高有效位指数据最左边的一位数,最低有效位指最右边的那一位数

- 高地址是数字大的,低地址是数字小的。

04讲(数据的基本运算)

词汇

ASCII,ASCII(American Standard Code for Information Interchange,美国信息交换标准代码

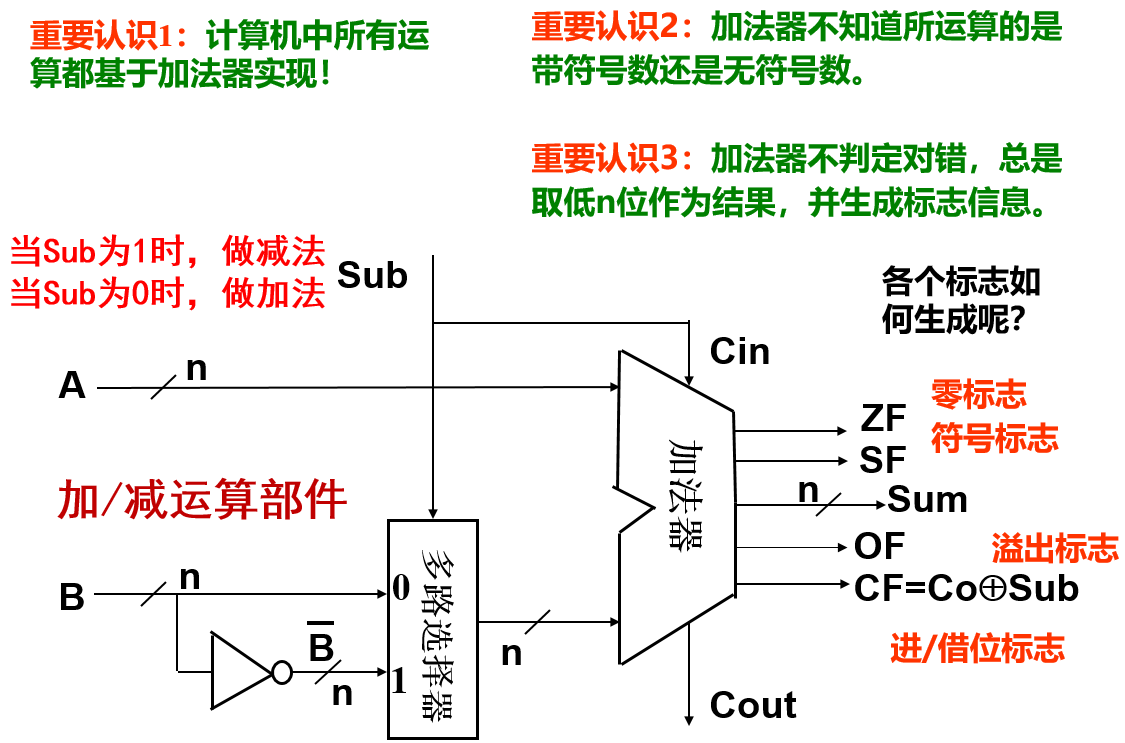

ZF,零标志,Zero Flag

OF,溢出标志,Overflow Flag

CF,进/借位标志,Carry Flag

SF,符号标志,Sign Flag

FA,全加器,Full Adder

HA,半加器,Half Adder

RCA,行波进位加法器,ripple carry adder

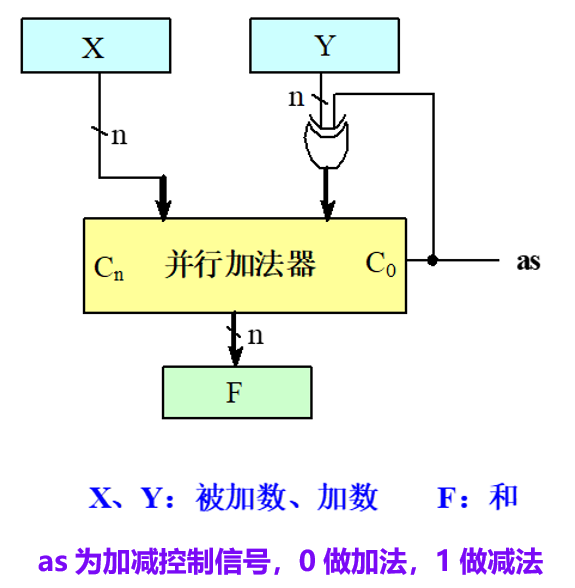

CAS,可控加减单元,Controllable Adder Subtracter

CLA,先行进位发生器,carry look-ahead

问题:

1.理解并简单解释本讲介绍的典型电路?

2.补码加减法电路示意图?

3.对2求补器电路?

05讲(程序转换概述,初步认识ISA)

词汇

MAR(AR):Memory Address Register,地址寄存器

MDR(DR): Memory Data Register,数据寄存器

IR:Instruction Register,指令寄存器

GPRs:General Purpose Registers,通用寄存器

ACC:Accumulator,累加器

OP:操作码,Operation Code

CISC:Complex Instruction Set Computer,复杂指令系统计算机

RISC:Reduced Instruction Set Computer,精简指令系统计算机

RTL:Register Transfer Level,寄存器传输级

问题:

1.RR、RM、MM是什么?

- RR结构:寄存器-寄存器结构(Register-Register)

- RM结构:寄存器-存储器结构(Register-Memory)

- MM结构:存储器-存储器结构(Memory-Memory)

06讲(IA-32指令系统概述)

词汇

IA:Intel Architecture,Intel架构

07讲(MIPS体系结构1)

词汇

MIPS:Microprocessor without Interlocked Pipeline Stages,无内部互锁流水级的微处理器

MIPS:Million Instructions Per Second),每秒处理百万指令数

问题:

1.简单MIPS程序?

08讲(MIPS体系结构2)

问题:

1.简单MIPS程序?

2.伪指令和伪操作的区别?

- 伪操作(directive)不会被编译器编译为机器指令,

- 伪指令(pseudo-instruction)会编译为机器指令。

09讲(ARM汇编)

词汇

ARM:Advanced RISC Machine,高级RISC处理机

IP:知识产权,intellectual property

GNU:通用公共许可证,GNU General Public License

10讲(程序执行概述,CPU结构和功能)

词汇

PSW:Program Status Word,程序状态字

问题:

1.现代CPU的组成?

现代CPU一般由运算器、控制器、数据通路(datapath)和高速缓冲存储器(Cache)组成。

——数据通路是指各部件之间通过数据线的相互连接。

——选择什么样的数据通路,对于CPU的性能有很大的影响。

2.CPU控制器的基本组成?

- 程序计数器(PC)

- 指令寄存器(IR)

- 指令译码器(ID)

- 时序发生器

- 操作控制器

3.运算器的基本组成?

- 算术逻辑单元(ALU)

- 累加寄存器(AC)或通用寄存器

- 数据寄存器(DR)

- 程序状态字寄存器(PSW)

4. CPU中的主要寄存器?

- 指令寄存器(IR)

- 程序计数器(PC)

- 地址寄存器(AR)

- 数据寄存器(DR)

- 累加寄存器(ACC)或GPRs

- 程序状态字寄存器(PSW)

5.CPU的具体功能?

- 指令控制:控制程序的顺序执行

- 操作控制:产生完成每条指令所需的控制命令

- 时间控制:对各种操作加以时间上的控制

- 数据加工:对数据进行算术运算和逻辑运算

- 中断处理:处理运行过程中出现的异常情况和特殊请求

11讲(datapath)

问题:

指令周期、机器周期、时钟周期?

1.指令周期

指令周期是取出一条指令并执行这条指令的时间。一般由若干个机器周期组成,是从取指令、译码到执行完所需的全部时间。

**一条指令的执行过程包括3个基本步骤: **

取指令:从存储器取出一条指令,该指令的地址由程序计数器PC给出。

译码:对该指令的操作码进行译码分析,确定是哪一种指令,并转到这种指令对应的执行阶段。

执行:按指令操作码的要求执行该指令。执行过程可能需要多步操作,控制器将为之形成完成该指令功能所需要的操作控制信号。执行完毕后,回到取指令阶段,去取下一条指令。如此反复,直到整个程序执行完。

2.机器周期

- 通常把一条指令周期划分为若干个机器周期,每个机器周期完成一个基本操作。

- 可以用主存的工作周期(存取周期)为基础来规定机器周期,比如,可以用CPU读取一个指令字的最短时间来规定机器周期

- 不同的指令,可能包含不同数目的机器周期。

- 一个机器周期中,包含若干个节拍脉冲或T脉冲。

- 机器周期的定义和规定,不同的计算机中规定不同

3.时钟周期

- 在一个机器周期内,要完成若干个微操作。这些微操作有的可以同时执行,有的需要按先后次序串行执行。因而需要把一个机器周期分为若干个相等的时间段,每一个时间段称为一个节拍脉冲或T周期。

- 时钟周期通常定义为机器主频的倒数。

12讲(单周期及多周期CPU构造)

13讲(流水线技术1)

问题:

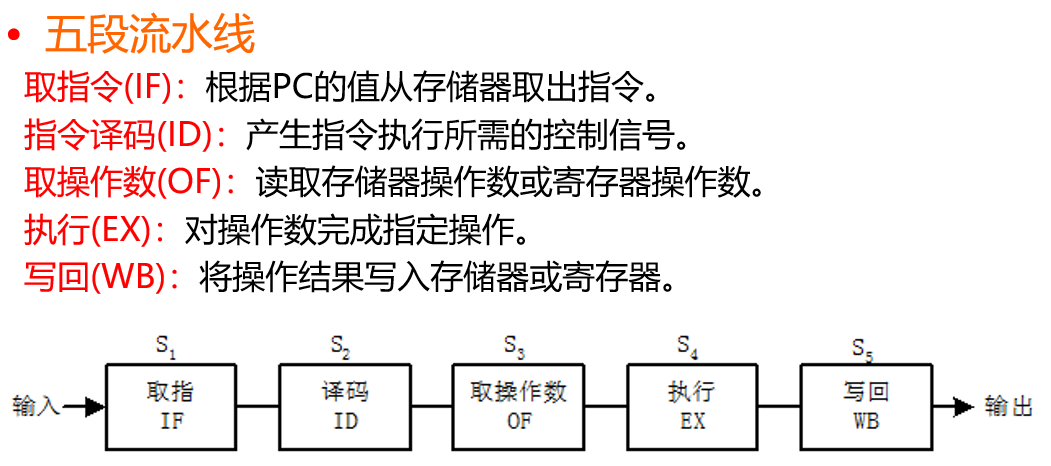

1.给出五段流水线示意图(段里面给出名称)?

2.流水线冲突有哪几种情况(结构,数据,控制)?

结构冲突:因硬件资源满足不了指令重叠执行的要求而发生的冲突。

数据冲突:当指令在流水线中重叠执行时,因需要用到前面指令的执行结果而发生的冲突。

控制冲突:流水线遇到分支指令和其他会改变PC值的指令所引起的冲突。

3.流水线时空图(吞吐率、加速比和效率)?

吞吐率(throughput):在单位时间内流水线所完成的任务数量或输出结果的数量。

加速比:完成同样一批任务,不使用流水线所用的时间与使用流水线所用的时间之比。

流水线的效率:流水线中的设备实际使用时间与整个运行时间的比值,即流水线设备的利用率。

14讲(流水线技术2)

词汇

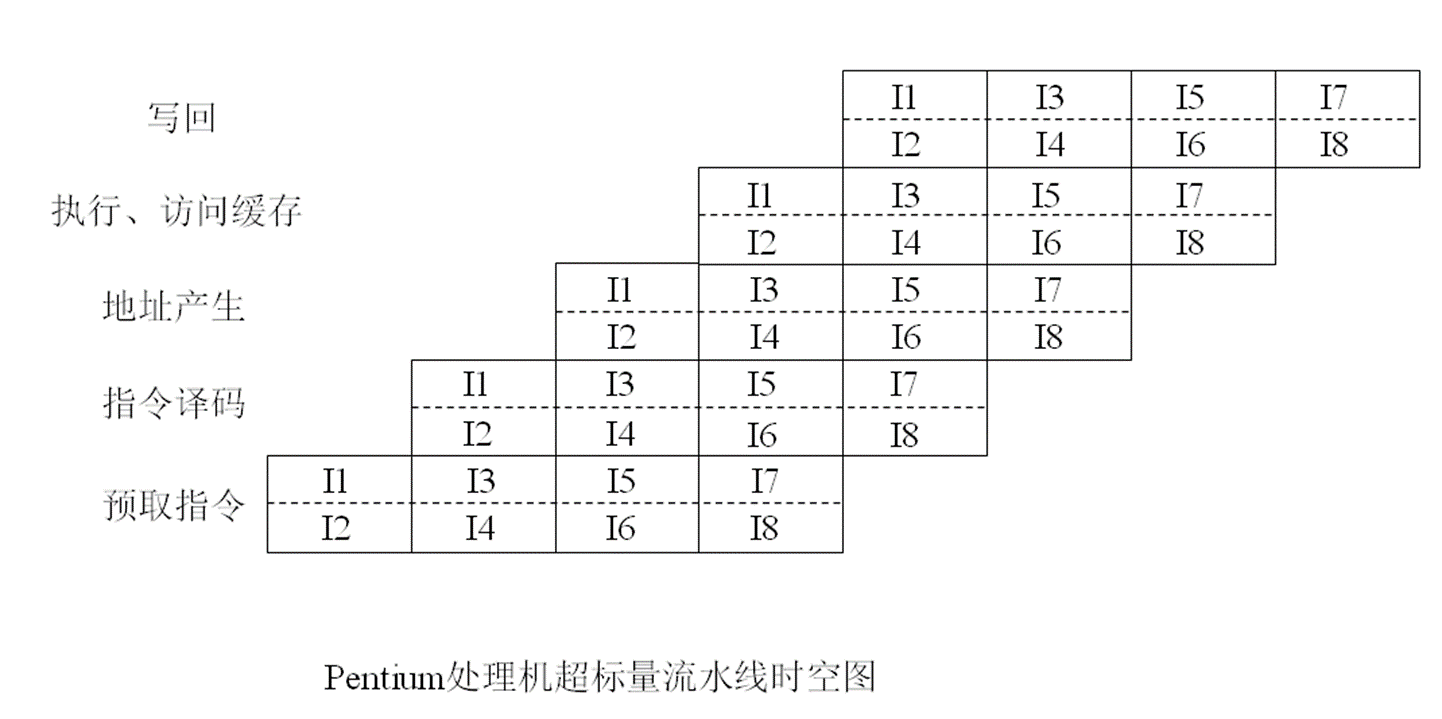

ILP:Instruction-Level-Parallelism,指令级并行

问题:

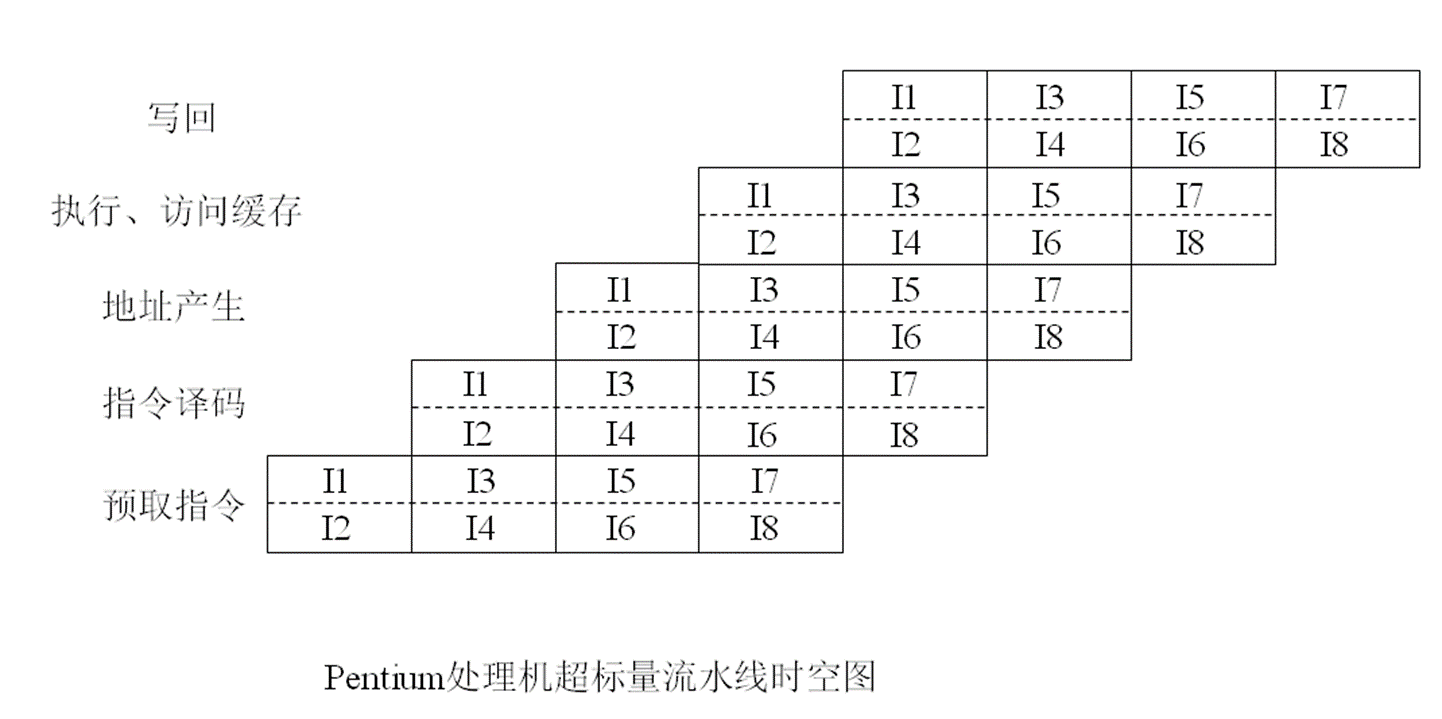

1.超标量处理机(时空图)?

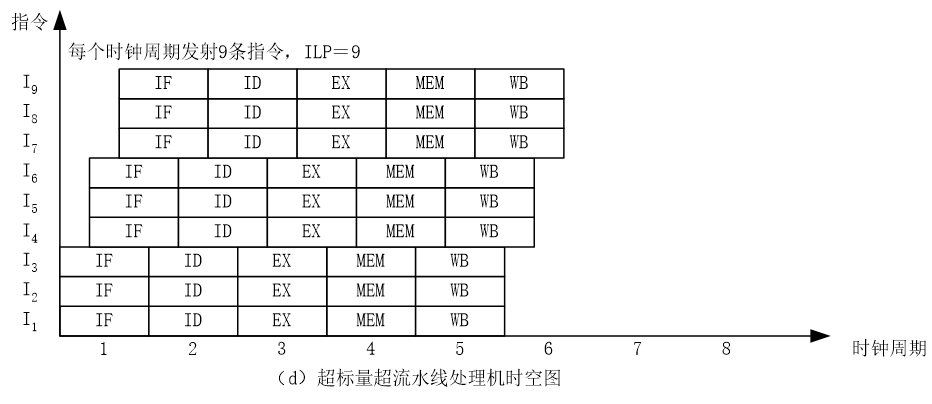

2.超流水线处理机(时空图)?

3.超标量超流水线处理机(时空图)?

15讲(总线技术)

词汇

ISA:工业标准总线,Industry Standard Architecture

PCI:外部设备部件互连,Peripheral Component Interconnect

问题:

1.总线分类?

总线分类1

① 内部总线:CPU内部连接各寄存器及运算器部件之间的总线

② 系统总线:CPU和计算机系统中其他高速功能部件相互连接的总线

③ I/O总线:CPU和中低速I/O设备相互连接的总线

④ 通信总线

总线分类2

① 数据总线

② 地址总线

③ 控制总线

④ 电源总线

总线分类3

① 并行总线

② 串行总线

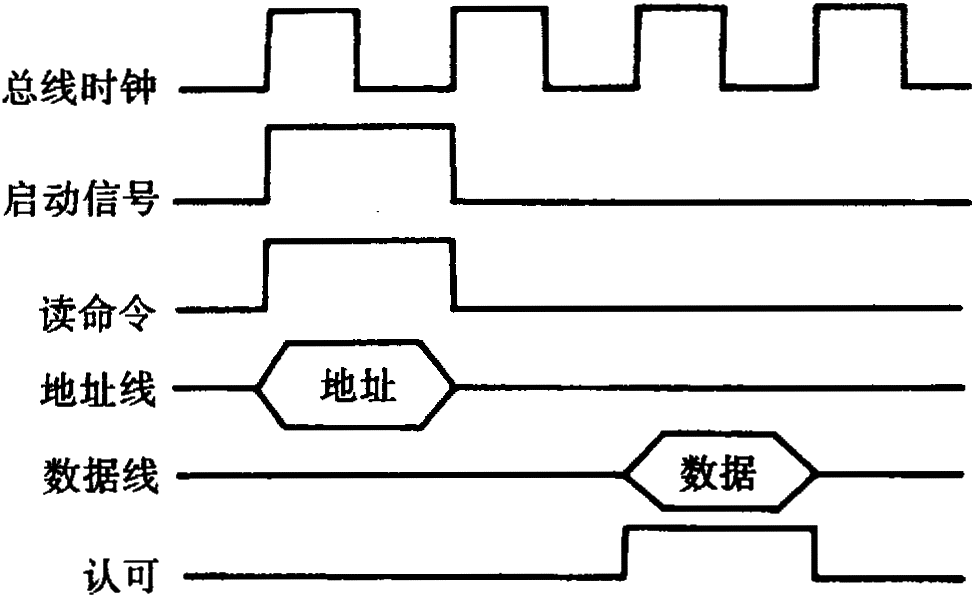

2.总线的一次信息传送过程,大致分为哪几个阶段? 若采用同步定时协议,请画出读数据的时序图来说明。

分五个阶段:请求总线,总线仲裁,寻址(目的地址),信息传送,状态返回(错误报告)

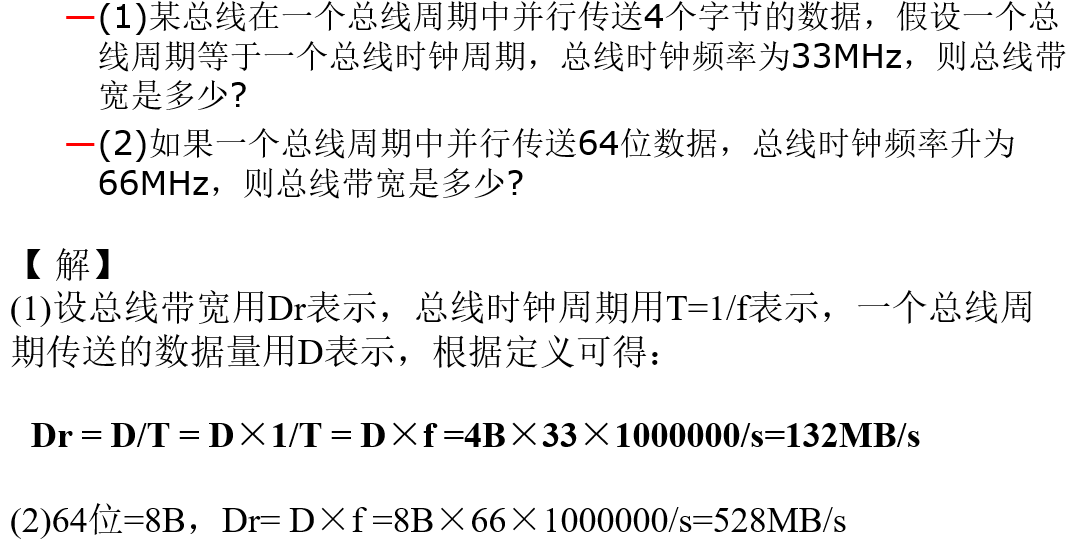

3.总线带宽计算?

总线带宽

总线带宽定义为总线本身所能达到的最高传输速率,它是衡量总线性能的重要指标

总线宽度

又称位宽,指的是总线同时传送数据的位数

总线频率

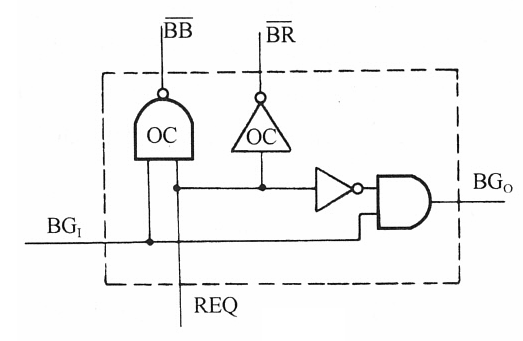

4.链式查询电路单元的逻辑图?

- BG(Bus Granted)

- BB(Bus Busy)

- BR(Bus Request)

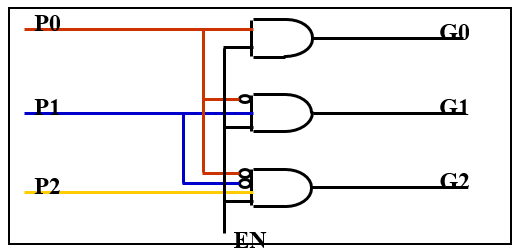

5.并行判优电路图

16讲(微程序与硬布线)

问题:

1.微程序控制器组成部分?

微程序控制器主要由控制存储器、微指令寄存器和地址转移逻辑三大部分组成。

17讲(半导体存储器)

词汇

ROM(Read-Only Memory,只读存储器)

RAM(Random-Access Memory,随机存取存储器)

EPROM(Erasable Programmable Read-Only Memory,可擦可编程只读存储器)

EEPROM(Electrically Erasable Programmable read only memory,电可擦可编程只读存储器)

SRAM(Static Random Access Memory,静态随机存取存储器)

DRAM(Dynamic Random Access Memory,动态随机存取存储器)

问题:

1.存储器的片位扩展?

复杂而且重要,看PPT吧,实在不行问老师。

18讲(磁存储与光存储)

词汇

CAV,constant angular velocity,恒定角速度

CLV,constant linear velocity,恒定线速度

CRC:循环冗余校验码

ECC:Error Checking and Correcting

问题:

1.磁记录的几种方式(列出即可)?

① 不归零制(NRZ0)

② 见“1”就翻不归零制(NRZ1)

③ 调相制(PM)

④ 调频制(FM)

⑤ 改进调频制(MFM)

19讲(高速缓冲存储器1)

问题:

1.三种映射方式分析?

① 直接(direct):每个主存块映射到cache的固定行中

② 全相联(full associate):每个主存块映射到cache的任意行中

③ 组相联(set associate):每个主存块映射到cache的固定组的任意行中

20讲(高速缓冲存储器2)

问题:

1.cache命中率、平均访问时间、效率的分析?

2.写回、写直达的区别?

21讲(虚拟存储器)

词汇

VM,虚拟存储器,Virtual Memory

VA,虚拟地址,Virtual Address

LA,逻辑地址,Logical Address

PA,物理地址,Physical Address

TLB,快表,translation lookaside buffer

问题:

1.TLB的作用?

(又称为快表技术。由于“页表”存储在主存储器中,查询页表所付出的代价很大,由此产生了TLB。TLB是一个小的,虚拟寻址的缓存,其中每一行都保存着一个由单个页表项组成的块。如果没有TLB,则每次取数据都需要两次访问内存,即查页表获得物理地址和取数据。TLB和CPU里cache之间不存在本质的区别,都是半导体硬件,只不过前者缓存页表数据,而后两个缓存实际数据。)

22讲(RAID及其它)

词汇

RAID:廉价磁盘冗余阵列,Redundant Array of Inexpensive Disks;或Redundant Arrays of Independent Disks,独立磁盘冗余阵列

SCSI:Small Computer System Interface,小型计算机系统接口)

23讲(中断)

问题:

1.CPU管理外围设备有几种方式?

① 程序查询方式:好处是硬件结构简单,不足是太浪费CPU时间,目前除单片机外,很少使用查询方式。

② 程序中断方式:是管理I/O操作的一个比较有效的方法。

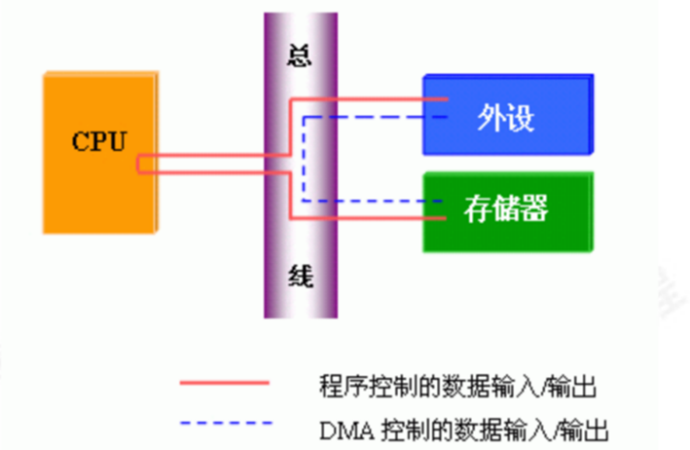

③ 直接内存访问(DMA)方式:是一种完全由硬件执行I/O交换,DMA控制器接管总线的控制,数据交换不经过CPU,适用于内存和高速外围设备之间大批数据交换的场合。

④ 通道方式:通道是一个具有特殊功能的处理器。

⑤ 外围处理机(PPU,Peripheral processing unit)方式:PPU基本上独立于主机工作,是通道方式的进一步发展。

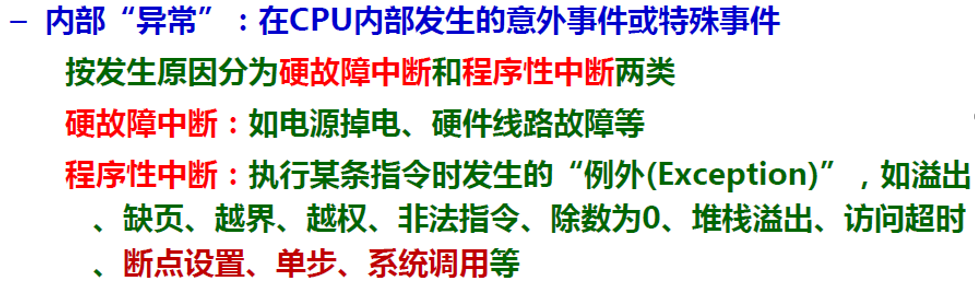

2.程序内部异常的原因?

3.程序外部中断的原因?

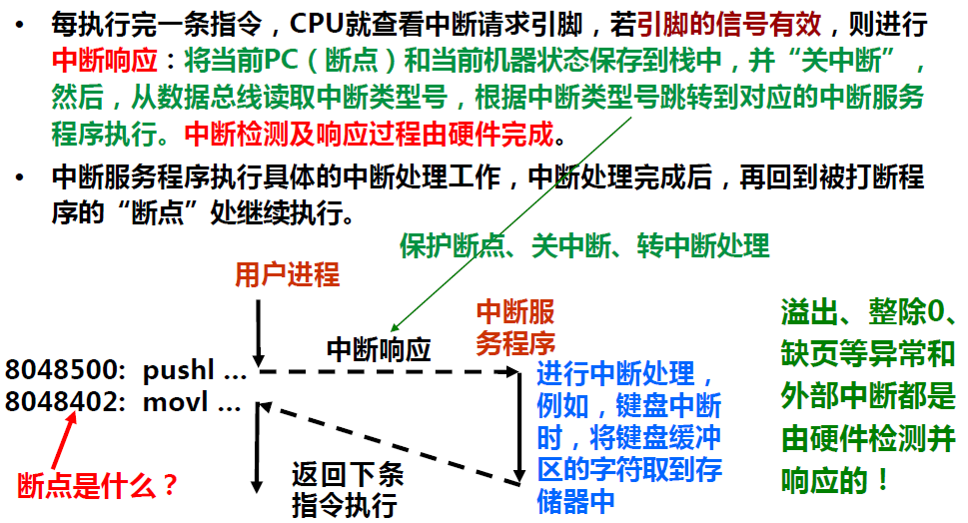

4.简述中断服务程序的流程?

5.中断屏蔽码的应用?

在CPU的中断管理部件中必须有一个中断屏蔽触发器,它可以在程序的控制下置“1”(设置屏蔽),或置“0”(取掉屏蔽)。只有在中断屏蔽标志为“0”时,CPU才可以受理中断。

24讲(DMA)

词汇

DMA:Direct Memory Access,直接存储器访问

问题:

1.DMA功能示意图?

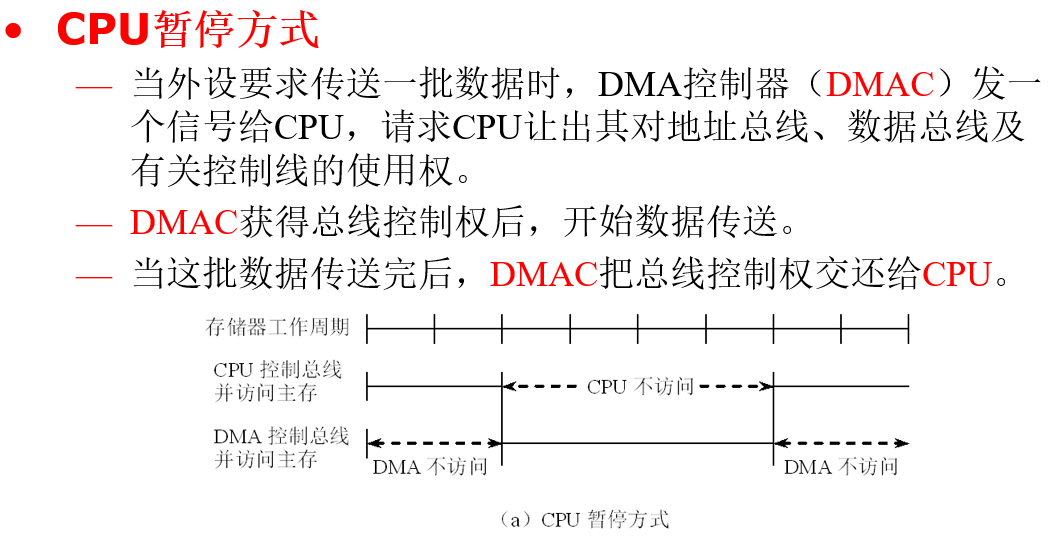

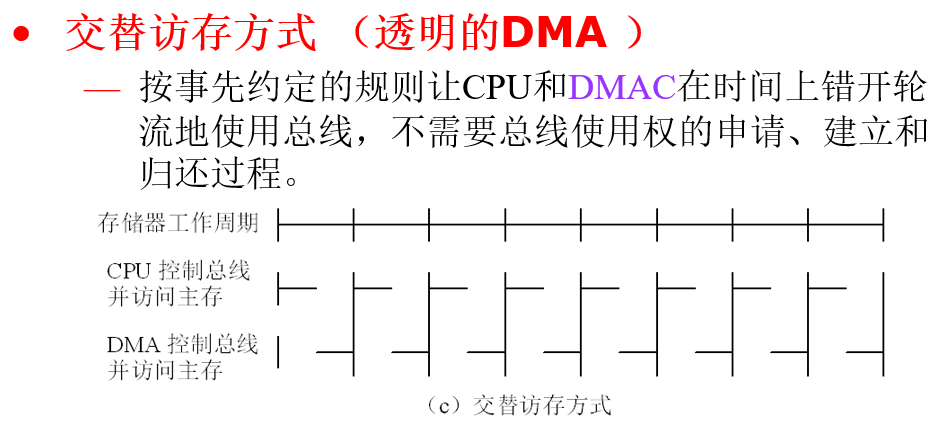

2.DMA传送的三种方式?

25讲(通用IO接口标准,芯片组,外部设备)

词汇

ATA:AT Attachment,AT计算机附加设备

PATA(并行ATA,Parallel ATA)

SATA(串行ATA,Serial ATA)

VGA:Video Graphics Array,视频图形阵列

DVI:Digital Visual Interface,数字视频接口

HDMI:High Definition Multimedia Interface,高清晰度多媒体接口

LCD:Liquid Crystal Display,液晶显示器

LED:Light Emitting Diode,发光二极管

26讲(并行计算,计算机系统性能评价)

词汇

SISD:单指令流单数据流

SIMD:单指令流多数据流

MIMD:多指令流多数据流

HPC:高性能计算,High Performance Computing

SC:超级计算,Super Computing

COW:工作站机群,Cluster of Workstation

PVP:并行向量机,Parallel Vector Processor

UMA:Uniform Memory Access,共享存储器架构

SMP:Symmetrical Multi-Processing,对称多处理器结构

NUMA:Non Uniform Memory Access Architecture,非一致内存架构

MPP:Massive Parallel Processing,海量并行处理结构

UMA:均匀存储器存取,Uniform Memory Access

NUMA:非均匀存储器存取,Non-uniform Memory Access

COMA:只用高速缓存的存储器结构(Cache-Only Memory Architecture),是NUMA的特例

问题:

1.从系统架构来看,目前的商用服务器大体可以分为三类

① 对称多处理器结构(SMP:Symmetric Multi-Processor)

② 非一致存储访问结构(NUMA:Non-Uniform Memory Access)

③ 海量并行处理结构(MPP:Massive Parallel Processing)

2.共享存储型多处理机有两种模型

- 均匀存储器存取(Uniform Memory Access,简称UMA)模型

- 非均匀存储器存取(Nonuniform Memory Access,简称NUMA)模型

27讲(GPU,树莓电脑硬件探密)

词汇

GPU:图形处理器,Graphics Processing Unit